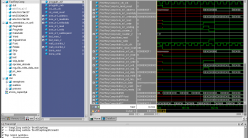

Diagram Rangkaian Penjumlah Penuh (Full Adder) (lihat gambar 1)

Gambar 1. Diagram Full Adder

Bagian ini akan menjelaskan beberapa tahapan, diantaranya :

- Membangun penjumlah penuh dari dua penjumlah separuh (half adder)

- Menggunakan VHDL perancangan model struktural

- Merealisasikan rancangan menggunakan perancangan hirarki (merancanga penjumlah separuh, menghubungkan beberapa penjumlah separuh, dan termasuk bebrapa logik tambahan)

Perancangan VHDL menggunakan Component

- Tentukan logik sub rangkaian (terdiri dari component) yang akan digunakan dalam perancangan hirarki.

- Definisikan antarmuka pada sub rangkaian, dengan cara menggunakan format yang sama dengan pernyataan Entity.

- Sub rangkaian dihubungkan menggunakan wire, dikenal sebagai structural VHDL.

- Pernyataan architecture untuk sub rangkaian dapat terdiri dalam file yang sama sebagai rancangan tingkat teratas atau dalam file yang terpisah. Jika terdiri dalam file yang terpisah, harus dikompile terlebih dahulu.

Format pernyataan komponen dalam VHDL dituliskan sebagai,

COMPONENT <nama komponen>

PORT ( <signal antarmuka> : tipe mode ) ;

END COMPONENT ;

Awal penulisan instantiation komponen dapat dituliskan sebagai,

<nama instance> : <nama komponen>

PORT MAP ( <nama port komponen> => <nama signal> ) ;

<nama instance> : <nama komponen>

PORT MAP ( <nama signal> ) ;

Diagram skematik ditunjukkan pada gambar 2.

VHDL untuk entity penjumlah penuhnya :

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

ENTITY fulladd IS

PORT ( Cin, A, B : IN STD_LOGIC ;

Sum, Cout : OUT STD_LOGIC ) ;

END fulladd ;

Gambar 3 menunjukkan identitas dari architecture penjumlah penuh,

VHDL dari rangkaian gambar 3 sebagaimana berikut :

ARCHITECTURE Struktur OF fulladd IS

SIGNAL s1, c1, c2: STD_LOGIC ;

COMPONENT halfadd

PORT ( A, B : IN STD_LOGIC ;

Sum, Cout : OUT STD_LOGIC ) ;

END COMPONENT ;

BEGIN

ha1 : halfadd PORT MAP ( A => A, B => B, Sum => s1, Cout => c1 ) ;

ha2 : halfadd PORT MAP ( A, B, Sum, c2 );

Cout <= c1 OR c2 ;

END ;