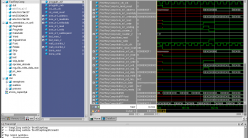

Diagram ripple carry ditunjukkan pada gambar 1.

Gambar 1. Ripple Carry

secara khusus dapat digambarkan menurut gambar 2.

Sehingga dengan mengasumsikan full adder yang dibentuk secara struktural dari beberapa half adder maka VHDL dari ripple carry ini sebagaimana berikut,

library ieee;

use ieee.std_logic_1164.all;

use work.pack.all;

ENTITY addbit IS

PORT (a : IN std_logic_vector(2 downto 0);

b : IN std_logic_vector(2 downto 0);

cin : IN std_logic;

s : OUT std_logic_vector(2 downto 0);

cout : OUT std_logic);

END;

ARCHITECTURE struktural OF addbit IS

SIGNAL cin1, cin2: std_logic;

BEGIN

fa0: fa PORT MAP(a(0),b(0), cin, s(0), cin1 );

fa1: fa PORT MAP(a(1),b(1), cin1, s(1), cin2 );

fa2: fa PORT MAP(a(2),b(2), cin2, s(2), cout );

END;

atau bisa juga menggunakan deskripsi architecture yang lebih singkat lagi, dengan cara menuliskan kode VHDL-nya sebagai berikut,

ARCHITECTURE struktural OF addbit IS

SIGNAL cy : std_logic_vector (3 downto 0);

BEGIN

Penjumlah:

FOR i IN 0 TO 2 GENERATE

myfa:fa PORT MAP(a(i),b(i),cy(i),s(i),cy(i+1));

END GENERATE;

cout <= cy(3);

cy(0) <= cin;

END;

Rangkaian carry ripple sangat lambat pewaktuannya karena banyaknya penyambungan per langkah blok rangkaian penjumlah separuhnya, sehingga untuk mengatasi hal ini bisa menggunakan metode pipelining, retiming atau dengan cara bus. Namun, cara yang paling sering digunakan adalah pipelining.