Penambahan proyek menggunakan masukan VHDL baru dapat dilakukan dengan memilih new source di proyek, kemudian memilih jenis modul VHDL baru dan nama entity.

Desain yang dibuat untuk membuat keluaran 8 LED berkedip pada FPGA Spartan 3E Starter Kit secara berurutan. Clock digunakan untuk men-trigger sinyal agar berlaku proses sekuensial yang ditandai dengan keluaran LED. Frekuensi clock yang terdapat pada FPGA Spartan 3E starter kit adalah 50 MHz (waktunya 20 ns), clock ini kemudian akan di buat menjadi 1 detik dengan menambahkan clock divider.

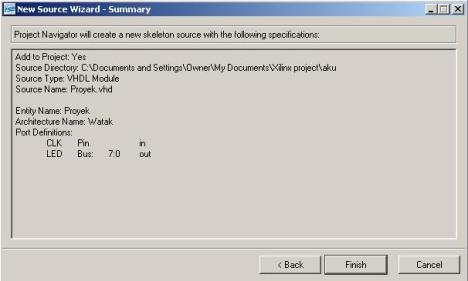

Pilih next, kemudian akan muncul ringkasan dari proyek yang dibuat.

Pilih next, kemudian akan muncul ringkasan dari proyek yang dibuat.

VHDL yang dibuat dengan entity di atas adalah:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; —- Uncomment the following library declaration if instantiating —- any Xilinx primitives in this code. –library UNISIM; –use UNISIM.VComponents.all; entity Proyek is Port ( CLK : in STD_LOGIC; LED : out STD_LOGIC_VECTOR (7 downto 0)); end ; architecture Watak of Proyek is signal poin: STD_LOGIC_VECTOR(7 DOWNTO 0):=”00000001″; signal counter: INTEGER:=0; constant counter_max: INTEGER:=49999999; begin process (CLK) is — Pembagi clock begin if rising_edge(CLK) then if counter<counter_max then counter<=counter+1; else counter<=0; end if; end if; end process; process (CLK) is begin if clk’EVENT and clk=’1′ then if counter=0 then poin<=poin(6 downto 0)&poin(7); end if; end if; end process; LED<=poin; end;